Microprocessor SPARClite

## omos **Peripheral LSI for SPARClite** MB86941/942

#### DESCRIPTION

MB86941 and MB86942 are dedicated peripheral LSIs for SPARClite\*. The MB86941 and MB86942 are designed to enable compact configuration of high-performance systems with SPARClite architecture, and provide the following features.

\*: SPARC is a registered trademark of SPARC International base on technology developed by Sun Microsystems, Inc. SPARClite is a trademark of SPARC International, Inc. licensed exclusively to Fujitsu Microelectronics, Inc.

#### ■ FEATURES

Direct connection to SPARClite

Register read/write in 2 clock cycles up to 30MHz. Register read/write in 3 clock cycles at 40MHz (MB86941) or 50MHz (MB86942).

Built-In On-Chip Modules:

Interrupt controller Interrupt input: 15 channels Each interrupt input has independent masking and trigger mode settings

16-bit timer: 4 channels Two of the four channels have prescalers Each channel has five independent mode operations MODE0 : Periodical-interrupt MODE1 : Timeout-interrupt MODE2 : Square wave generator

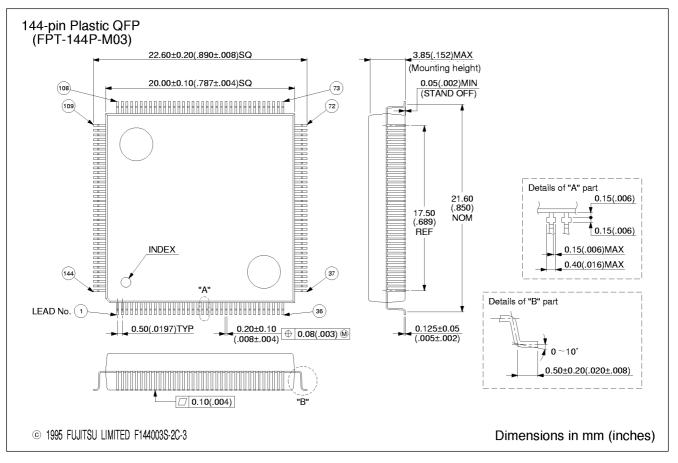

# (Continued) (Conti PACKAGE 144-pin Plastic QFP (FPT-144P-M03)

#### (Continued)

MODE3: Programmable one shot (software trigger) MODE4: Programmable one shot (external trigger)

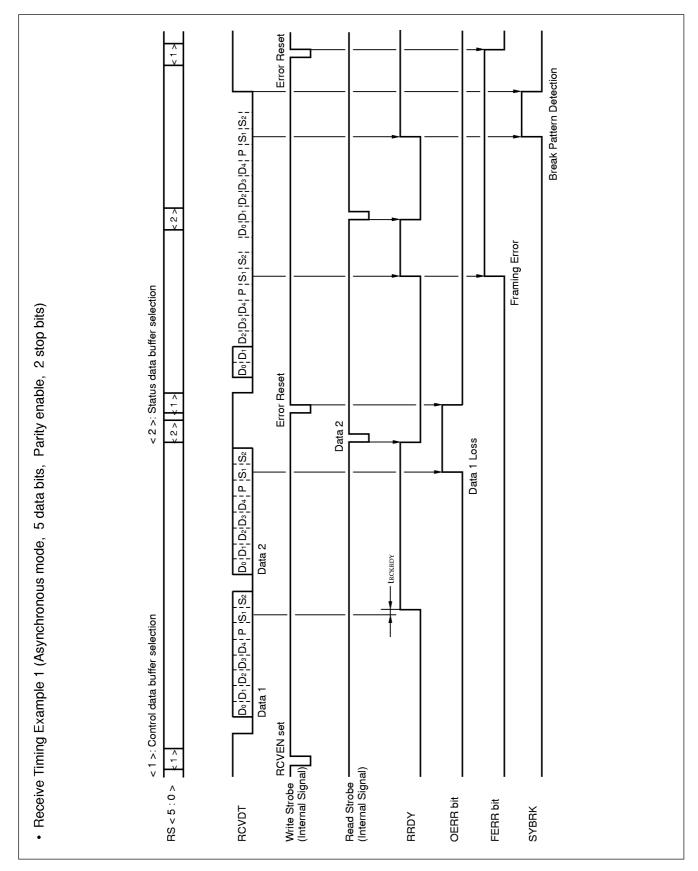

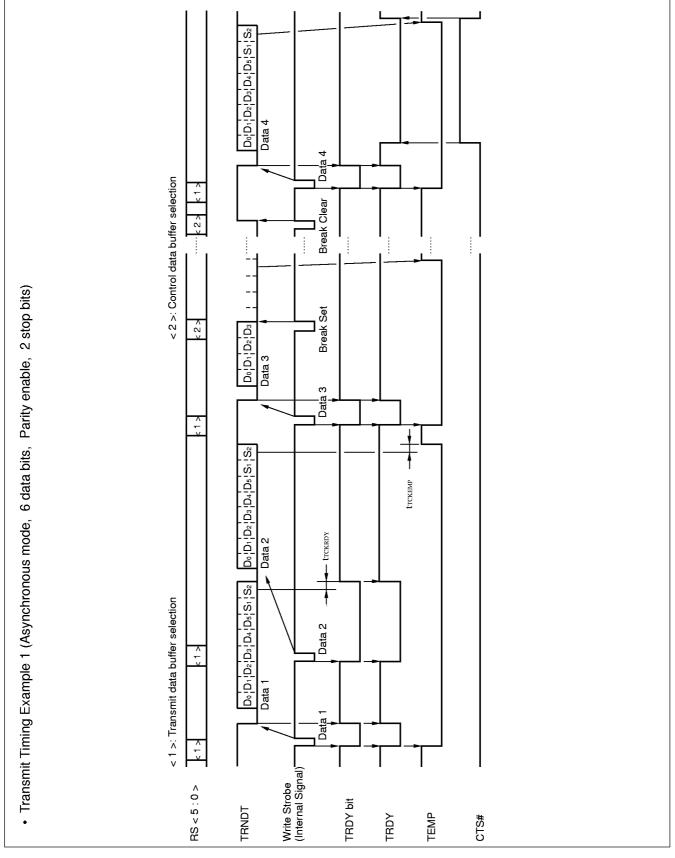

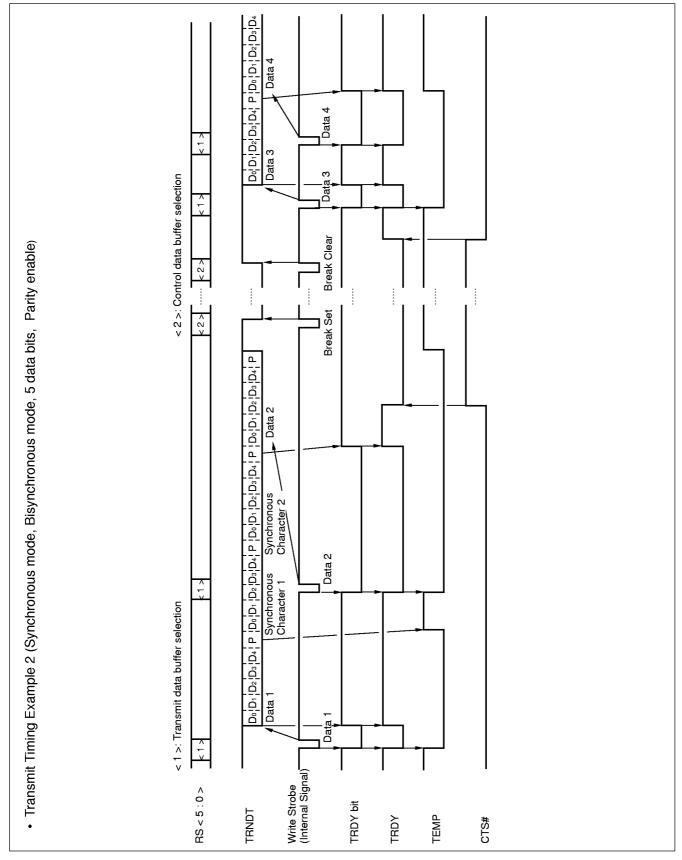

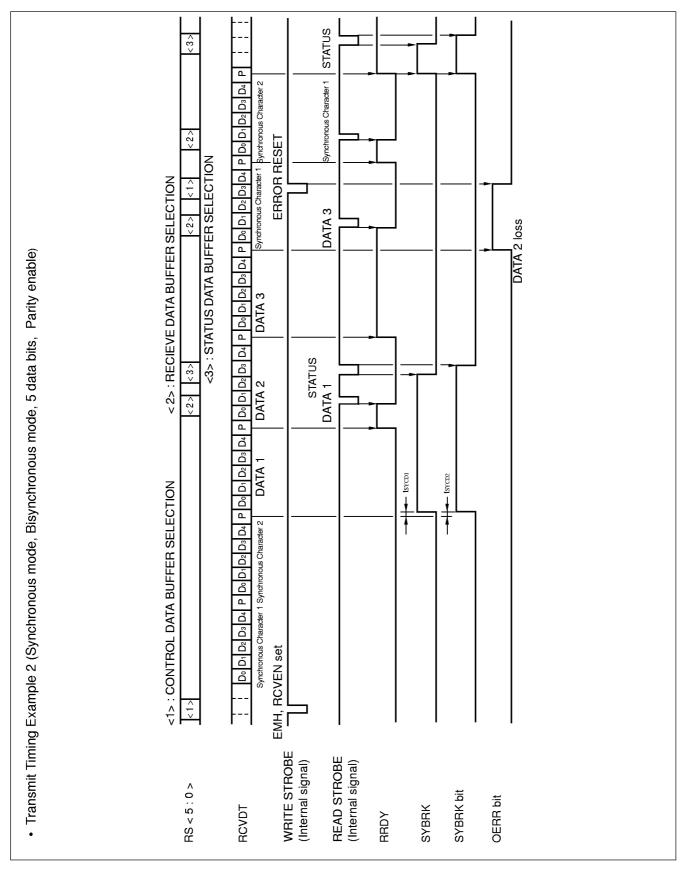

- SDTR (Serial data transmitter receiver): 2 channels MB89251A type

- Timing control, CS expansion Generates read, write and data strobe signals according to the requirements of external devices.

- SIO (Synchronous serial input/output) Simple synchronous type serial input/output

- I/O port, 16-bit Individual direction control by bit

5V single power supply (MB86941), 3.3V single power supply (MB86942) Upward pin compatibility with MB86940C

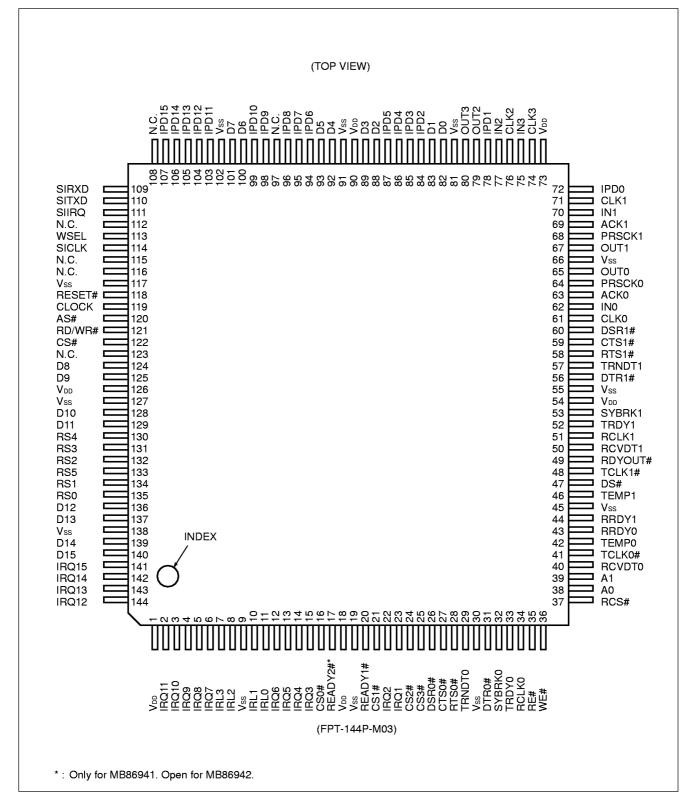

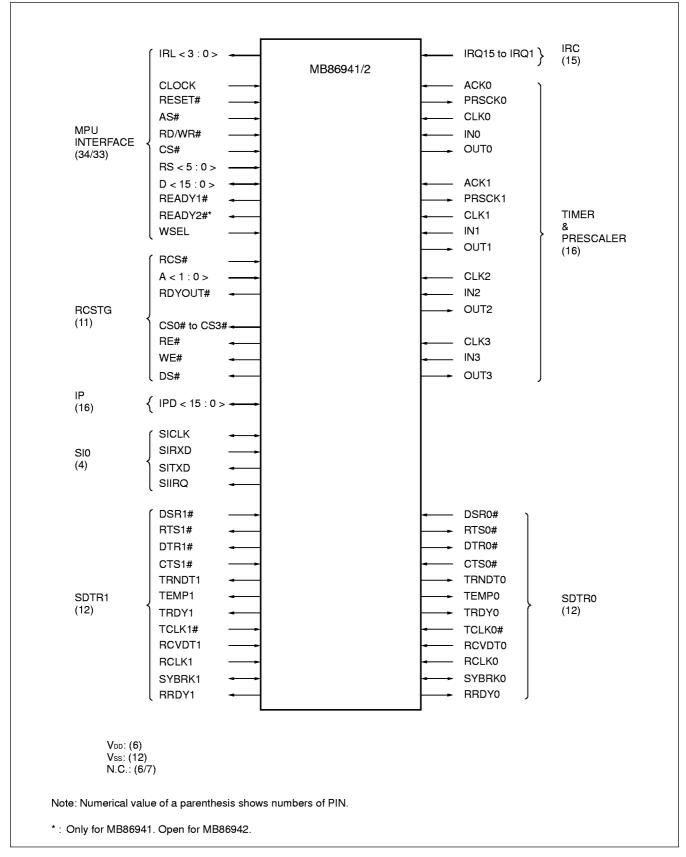

#### PIN ASSIGNMENT

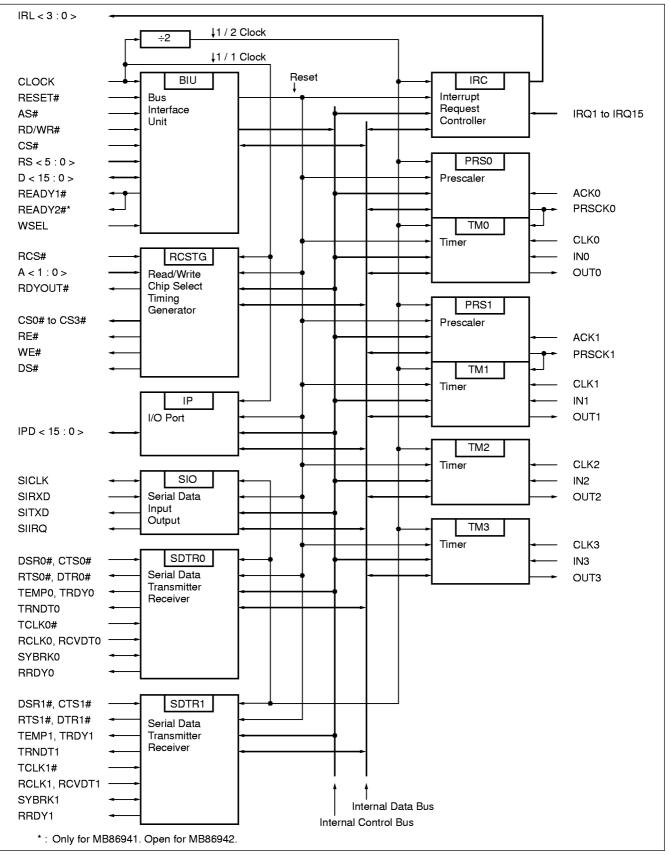

#### BLOCK DIAGRAM

4

#### ■ DESCRIPTION OF BLOCK FUNCTIONS

#### 1. BIU (Bus Interface Unit)

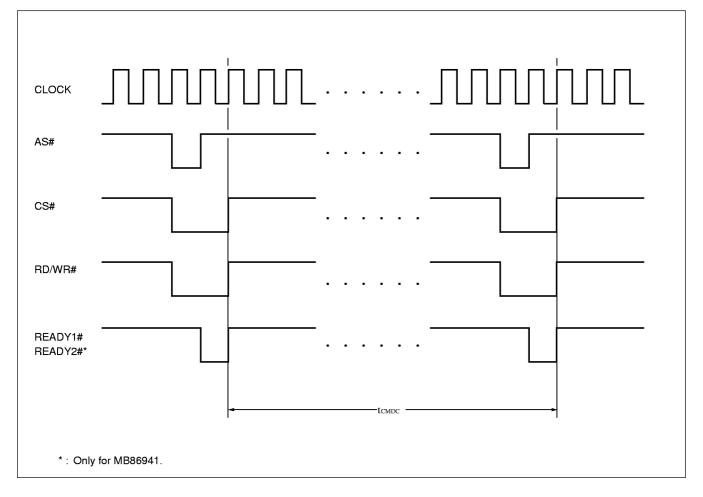

This block receives MPU (SPARClite) bus signals and bus controls signals (CLOCK, AS#, RD/WR#, CS#, ADR6 to ADR2, D<15:0>) and generates control signals for accessing MB86941/MB86942 internal resources. It also returns that Ready signal to the MPU which corresponds to the access time of each of such resources.

#### 2. IRC (Interrupt Request Controller)

This block provides 15-channel interrupt input signals to transmit the interrupt level IRL <3:0> for each interrupt to the SPARClite.

#### 3. TM (Timer) and PRS (Prescaler)

TM0 to TM3 are 16-bit timers serving as periodic interrupt generation timers, a watchdog timer, and an external event counter. The operating clock can be selected from among the internal clock, the clock frequency-divided by the prescaler, and the external clock.

Prescalers 0 and 1 are linked with timer channels 0 and 1, respectively. Each of the prescalers is initialized upon loading (or reloading) of the timer initial value of the corresponding timer.

#### 4. SDTR (Serial Data Transmitter Receiver)

SDTR0 and SDTR1 are serial data transmitter/receiver modules programmable for control of transmission and reception.

The programming model is the same as that for the MB89251A.

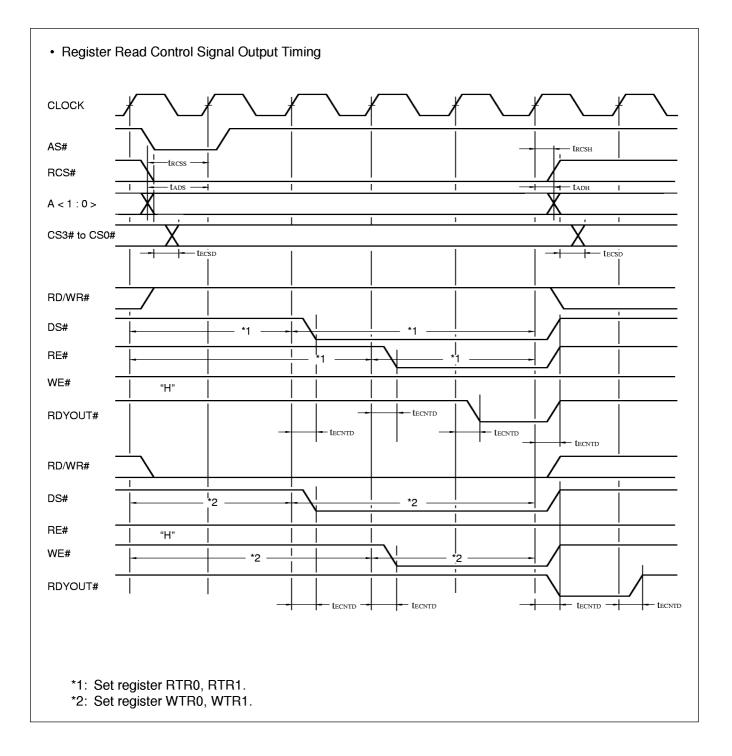

#### 5. RCSTG (Read/Write Timing Generator)

This module generates read, write, and data strobe signals conforming to the required timings for external connection of other devices. The assert timing and pulse width of each signal to be generated is programmable.

#### 6. IP (I/O Port)

There are 16 I/O ports. The input/output direction of each port can be set by the control register.

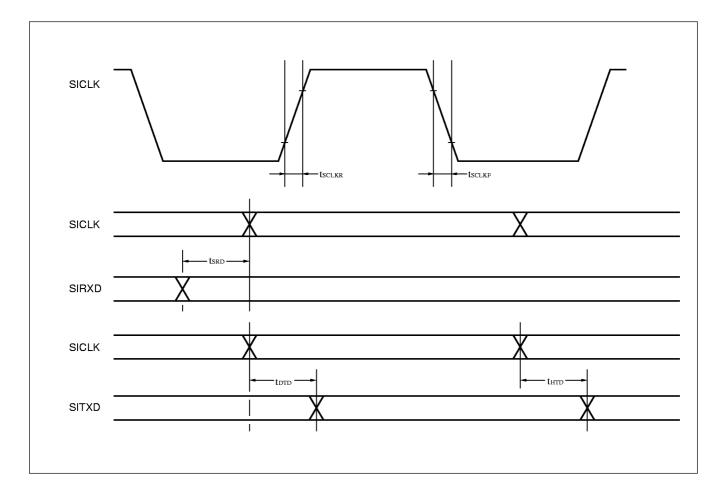

#### 7. SIO (Serial Data Input Output)

This block is a clock-synchronous serial interface. The transfer clock signal can be set to the internally generated or externally input one. The SIO outputs data to be transmitted and inputs received data in synchronization with the transfer clock signal.

#### ■ PIN DESCRIPTION

#### 1. MPU INTERFACE SIGNALS (34/33)

| Pin symbol | I/O | Pin no. | Pin name          | Description                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------|-----|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RESET#     | I   | 118     | Reset             | Reset input pin<br>Input an "L" signal to this pin to reset the chip.                                                                                                                                                                                                                       |  |  |  |  |

| CLOCK      | I   | 119     | Clock             | System clock input pin<br>The chip contains some modules that use the clock<br>signal from this pin (not divided), and other modules<br>that use the clock signal divided in half.<br>Clock not divided: BIU, RCSTG, IP<br>Clock divided: IRC, PRS0, PRS1, TM0 to TM3,<br>SDTR0, SDTR1, SIO |  |  |  |  |

| AS#        | I   | 120     | Address Strobe    | Address strobe input pin<br>Input an "L" signal to this pin to determine register<br>access according to the signals input to the RS<5:0>,<br>CS#, and RD/WR# pins.                                                                                                                         |  |  |  |  |

| RD/WR#     | Ι   | 121     | Read/Write        | Read/write input pin<br>Input an "H" signal to designate a read cycle, or an<br>signal to designate a write cycle.                                                                                                                                                                          |  |  |  |  |

| CS#        | I   | 122     | Chip Select       | Chip select input pin                                                                                                                                                                                                                                                                       |  |  |  |  |

| RS0        | Ι   | 135     | Register Select 0 |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RS1        | Ι   | 134     | Register Select 1 | Register select input pin                                                                                                                                                                                                                                                                   |  |  |  |  |

| RS2        | I   | 132     | Register Select 2 | The combination of input signals to the RS<5:0> and CS# pins determines which register is accessed.                                                                                                                                                                                         |  |  |  |  |

| RS3        | Ι   | 131     | Register Select 3 | The RS5 pin has internal pull-down resistance                                                                                                                                                                                                                                               |  |  |  |  |

| RS4        | Ι   | 130     | Register Select 4 | (MB86941 only).                                                                                                                                                                                                                                                                             |  |  |  |  |

| RS5        | I   | 133     | Register Select 5 |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| READY1#    | 0   | 20      | Ready 1           | Data ready output pin<br>MB86941: Open drain output with 12mA "L" drive<br>capability. Drives an "H" level signal for 3ns<br>before going to High-Z state.                                                                                                                                  |  |  |  |  |

| READY2#    | 0   | 17      | Ready 2           | MB86942: Normal output. READY2# signal deleted. If<br>the READY generator circuit in the MPU is<br>used, it is not necessary to connect this pin<br>to the MPU.                                                                                                                             |  |  |  |  |

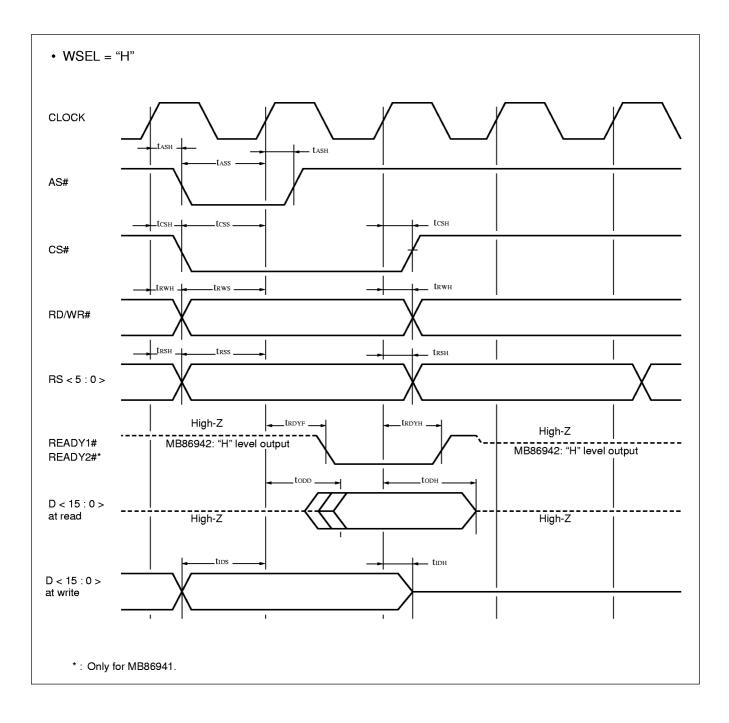

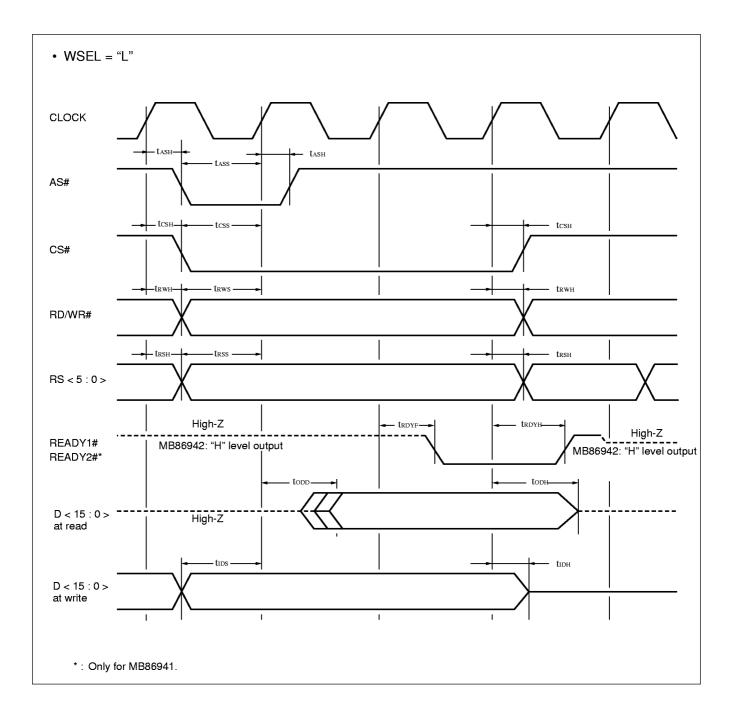

| WSEL       | I   | 113     | Wait Select       | Wait select input pin<br>Input to this pin determines the interface timing with<br>the MPU.<br>Fix "L" to set register read/write access to 3 cycles, or<br>fix "H" to set register read/write access to 2 cycles.<br>This pin has internal pull-up resistance (MB86941<br>only).           |  |  |  |  |

| Pin symbol | I/O | Pin no. | Pin name                     | Description                                                                           |  |  |

|------------|-----|---------|------------------------------|---------------------------------------------------------------------------------------|--|--|

| D0         | I/O | 82      | Data Bus 0                   |                                                                                       |  |  |

| D1         | I/O | 83      | Data Bus 1                   |                                                                                       |  |  |

| D2         | I/O | 88      | Data Bus 2                   |                                                                                       |  |  |

| D3         | I/O | 89      | Data Bus 3                   |                                                                                       |  |  |

| D4         | I/O | 92      | Data Bus 4                   |                                                                                       |  |  |

| D5         | I/O | 93      | Data Bus 5                   |                                                                                       |  |  |

| D6         | I/O | 100     | Data Bus 6                   |                                                                                       |  |  |

| D7         | I/O | 101     | Data Bus 7                   | Data I/O port                                                                         |  |  |

| D8         | I/O | 124     | Data Bus 8                   | These pins are used to transfer register read/write data.                             |  |  |

| D9         | I/O | 125     | Data Bus 9                   |                                                                                       |  |  |

| D10        | I/O | 128     | Data Bus 10                  |                                                                                       |  |  |

| D11        | I/O | 129     | Data Bus 11                  |                                                                                       |  |  |

| D12        | I/O | 136     | Data Bus 12                  |                                                                                       |  |  |

| D13        | I/O | 137     | Data Bus 13                  |                                                                                       |  |  |

| D14        | I/O | 139     | Data Bus 14                  |                                                                                       |  |  |

| D15        | I/O | 140     | Data Bus 15                  |                                                                                       |  |  |

| IRL0       | 0   | 11      | Interrupt Request<br>Level 0 |                                                                                       |  |  |

| IRL1       | 0   | 10      | Interrupt Request<br>Level 1 | Interrupt request output pin                                                          |  |  |

| IRL2       | 0   | 8       | Interrupt Request<br>Level 2 | These pins are used to generate interrupts to the MPU and notify the interrupt level. |  |  |

| IRL3       | 0   | 7       | Interrupt Request<br>Level 3 |                                                                                       |  |  |

#### 2. INTERRUPT REQUESTS (15)

| Pin symbol | I/O | Pin no. | Pin name             | Description                                                                                                   |  |  |  |  |

|------------|-----|---------|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IRQ1       | Ι   | 23      | Interrupt Request 1  |                                                                                                               |  |  |  |  |

| IRQ2       | I   | 22      | Interrupt Request 2  |                                                                                                               |  |  |  |  |

| IRQ3       | I   | 15      | Interrupt Request 3  | Interrupt request pin<br>Interrupt receiving priority: IRQ15 is highest priority                              |  |  |  |  |

| IRQ4       | I   | 14      | Interrupt Request 4  | and IRQ1 is lowest.                                                                                           |  |  |  |  |

| IRQ5       | I   | 13      | Interrupt Request 5  | A choice of four interrupt waveforms is available by mode setting for each of the 15 pins independently,      |  |  |  |  |

| IRQ6       | I   | 12      | Interrupt Request 6  | including "H" level, "L" level, rising edge, and falling                                                      |  |  |  |  |

| IRQ7       | I   | 6       | Interrupt Request 7  | edge.<br>Each input has a filtering function for short pulse                                                  |  |  |  |  |

| IRQ8       | I   | 5       | Interrupt Request 8  | signals, by which an interrupt request is recognized                                                          |  |  |  |  |

| IRQ9       | I   | 4       | Interrupt Request 9  | once a signal is detected at active level at three successive rising edges of the internal clock signal.      |  |  |  |  |

| IRQ10      | I   | 3       | Interrupt Request 10 | Once an interrupt request is detected, it passes                                                              |  |  |  |  |

| IRQ11      | I   | 2       | Interrupt Request 11 | through priority control and masking control and is<br>output at the IRL<3:0> pins as an interrupt request to |  |  |  |  |

| IRQ12      | I   | 144     | Interrupt Request 12 | the MPU.                                                                                                      |  |  |  |  |

| IRQ13      | Ι   | 143     | Interrupt Request 13 | If these pins are not used, they should be fixed at inactive level.                                           |  |  |  |  |

| IRQ14      | Ι   | 142     | Interrupt Request 14 |                                                                                                               |  |  |  |  |

| IRQ15      | Ι   | 141     | Interrupt Request 15 |                                                                                                               |  |  |  |  |

#### 3. TIMER SIGNALS (16)

| Pin symbol | I/O | Pin no. | Pin name                                             | Description                                                                                                                                                                                                                             |  |  |  |

|------------|-----|---------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLK0       | Ι   | 61      | CLK0 : Timer Clock 0                                 | Timer control signal pin<br>These pins are used to input an external clock signa                                                                                                                                                        |  |  |  |

| IN0        | Ι   | 62      | to<br>CLK3 : Timer Clock 3                           | to the timer.                                                                                                                                                                                                                           |  |  |  |

| OUT0       | 0   | 65      |                                                      | In external clock mode these signals are synchronized with the internal clock.                                                                                                                                                          |  |  |  |

| CLK1       | Т   | 71      | IN0 : Timer Input 0                                  | Input pin for count operation control signals to the timer                                                                                                                                                                              |  |  |  |

| IN1        | Ι   | 70      | to                                                   | In MODE0 through MODE3, the input signal is a gate                                                                                                                                                                                      |  |  |  |

| OUT1       | 0   | 67      | IN3 : Timer Input 3                                  | signal. In MODE4, the pins input an external trigger signal.                                                                                                                                                                            |  |  |  |

| CLK2       | T   | 76      |                                                      | Timer output pin                                                                                                                                                                                                                        |  |  |  |

| IN2        | I   | 77      | OUT0 : Timer Output 0<br>to<br>OUT3 : Timer Output 3 | <ul> <li>The output waveform is determined by the mode setting:</li> <li>Periodic signal waveform output</li> <li>Square wave output</li> <li>One-shot pulse waveform output</li> </ul>                                                 |  |  |  |

| OUT2       | 0   | 79      |                                                      |                                                                                                                                                                                                                                         |  |  |  |

| CLK3       | T   | 74      |                                                      |                                                                                                                                                                                                                                         |  |  |  |

| IN3        | I   | 75      |                                                      |                                                                                                                                                                                                                                         |  |  |  |

| OUT3       | 0   | 80      |                                                      | At reset, an "L" level signal is output.                                                                                                                                                                                                |  |  |  |

| ACK0       | I   | 63      | Asynchronous Clock 0                                 | Prescaler asynchronous clock pin<br>Input can be asynchronous with respect to the system<br>clock signal input at the CLOCK pin.<br>If an external clock signal is selected by the PRS0 and                                             |  |  |  |

| ACK1       | I   | 69      | Asynchronous Clock 1                                 | PRS1 registers, this signal can be used as a source<br>clock for the prescaler. The clock signal divided by the<br>prescaler is output at the PRSCK0, PRSCK1 pins.<br>If these pins are not used, they should be fixed at "L"<br>level. |  |  |  |

| PRSCK0     | 0   | 64      | Prescaler Clock Output 0                             | Prescaler clock output pin                                                                                                                                                                                                              |  |  |  |

| PRSCK1     | 0   | 68      | Prescaler Clock Output 1                             | An "L" level signal is output at reset.                                                                                                                                                                                                 |  |  |  |

#### 4. SDTR SIGNALS (24)

| Pin symbol | I/O | Pin no. | Pin name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSR0#      | Ι   | 26      | Data Set Ready 0      | Modem control signal DSR input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DSR1#      | Ι   | 60      | Data Set Ready 1      | The status of these pins is indicated at the status register bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTS0#      | 0   | 28      | Request To Send 0     | Modem control signal RTS output pin<br>Set the command register bit 5 to "1" to output an "L"                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RTS1#      | 0   | 58      | Request To Send 1     | signal, or to "0" to output an "H" signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DTR0#      | 0   | 31      | Data Terminal Ready 0 | These pins can be used as a DATA TERMINAL READY signal or a RATE SELECT signal of                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTR1#      | 0   | 56      | Data Terminal Ready 1 | modem.Set the command register bit 1 to "1" to output<br>an "L" signal, or to "0" to output an "H" signal.                                                                                                                                                                                                                                                                                                                                                                                                     |

| CTS0#      | I   | 27      | Clear To Send 0       | Modem CLEAR TO SEND pin<br>To enable sending, the command register bit 0 must                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CTS1#      | I   | 59      | Clear To Send 1       | be set to "1" and also an "L" level signal must be input at these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TRNDT0     | 0   | 29      | Transmit Data 0       | Transmit Data pin<br>Parallel data written to the data register is converted to<br>serial data and output from these pins.<br>In asynchronous mode, a start bit and stop bit are<br>attached, and a parity bit may be attached if<br>necessary.<br>If there is no data to be sent in the SDTR module, in<br>synchronous mode a synchronizing character is output<br>and in asynchronous mode the pins go to mark mode.<br>If a send-prohibited setting (command register bit 0 set                             |

| TRNDT1     | 0   | 57      | Transmit Data 1       | to "0") is in effect, or if an "H" signal is input at the<br>CTS# pin, these pins to mark mode. However if a<br>send-prohibited setting is entered while a sending<br>operation is in progress, all sending data already<br>written will be sent before these pins go to mark mode.<br>In addition, in bisynchronous mode if the first<br>synchronization character is being sent<br>(synchronization standby), then these pins will go to<br>mark mode after sending the second synchronization<br>character. |

| TEMP0      | ο   | 42      | Transmit Empty 0      | These pins indicate whether sending data is present.<br>If there is no data to be sent in the SDTR module, the                                                                                                                                                                                                                                                                                                                                                                                                 |

| TEMP1      | 0   | 46      | Transmit Empty 1      | signal level is "H."<br>As soon as one byte of sending data is written, these<br>pins go to "L" level at the fall of the write signal.                                                                                                                                                                                                                                                                                                                                                                         |

| TRDY0      | 0   | 33      | Transmit Ready 0      | Transmit Ready output pin<br>When the CTS# signal is "L" and the command                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TRDY1      | ο   | 52      | Transmit Ready 1      | register is set to enable sending, these pins send an<br>"H" level signal whenever the sending data buffer is<br>empty.                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin symbol | I/O | Pin no. | Pin name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

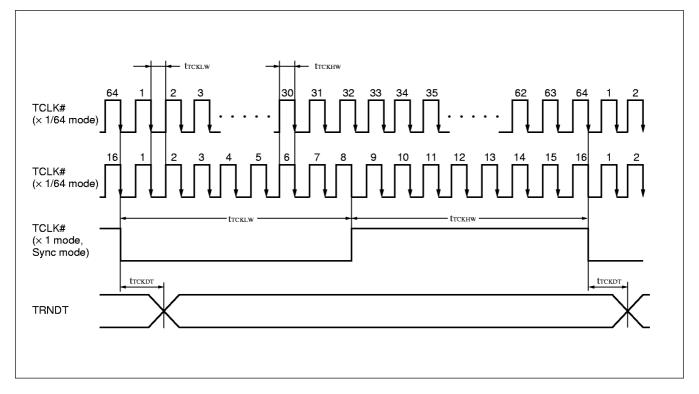

| TCLK0#     | I   | 41      | Transmit Clock 0 | Transmit Clock input pin<br>In synchronous mode, the sending bit rate is fixed at<br>the sending clock $\times 1$ , so that the clock signal input at<br>these pins becomes the sending bit rate.<br>In asynchronous mode, the sending bit rate will be the<br>sending clock signal $\times 1$ , or $\times 1/16$ , or $\times 1/64$ depending<br>on the bit rate acting in the mode                                                                                        |

| TCLK1#     | I   | 48      | Transmit Clock 1 | on the bit rate setting in the mode register.<br>For example, if a 19.2 kHz clock signal is input at the TCLK# pin, the sending bit rate will be 19200 pbs with an $\times$ 1 setting, or 1200 pbs with an $\times$ 1/16 setting, or 300 pbs with an $\times$ 1/64 setting.<br>Sending data is output in synchronization with the falling edge of the sending clock signal.                                                                                                 |

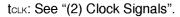

| RCVDT0     | Ι   | 40      | Receive Data 0   | Receive Data input pin<br>Serial data input to these pins is converted to parallel                                                                                                                                                                                                                                                                                                                                                                                          |

| RCVDT1     | I   | 50      | Receive Data 1   | data in the SDTR module and then can be read by the data bus.                                                                                                                                                                                                                                                                                                                                                                                                               |

| RCLK0      | I   | 34      | Receive Clock 0  | Receive Clock input pin<br>In synchronous mode, the receiving bit rate is fixed at<br>the receiving clock $\times 1$ , so that the clock signal input at<br>these pins becomes the receiving bit rate.<br>In asynchronous mode, the receiving bit rate will be<br>the sending clock signal $\times 1$ , or $\times 1/16$ , or $\times 1/64$<br>depending on the bit rate setting in the mode register.<br>For example, if a 19.2 kHz clock signal is input at the           |

| RCLK1      | I   | 51      | Receive Clock 1  | RCLK pin, the receiving bit rate will be 19200 pbs with<br>an $\times$ 1 setting, or 1200 pbs with an $\times$ 1/16 setting, or<br>300pbs with an $\times$ 1/64 setting.<br>Receiving data is sampled in synchronization with the<br>rising edge of the receiving clock signal.<br>Note that in asynchronous mode $\times$ 1 speed differs from<br>$\times$ 1/16 and $\times$ 1/64 speeds in that external<br>synchronization of the RCLK and RCVDT signals is<br>required. |

| Pin symbol | I/O | Pin no. | Pin name                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|-----|---------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

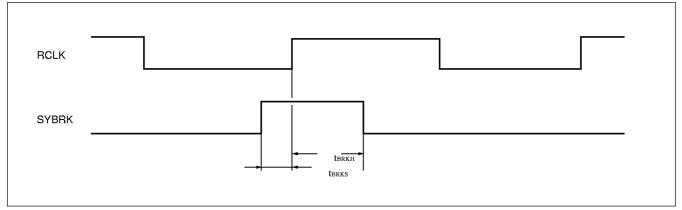

| SYBRK0     | I/O | 32      | Synchronous/Break<br>Detect 0 | <ul> <li>These pins can function as synchronization detect input, synchronization detect output, or break detect output pins, depending on the mode setting.</li> <li>External synchronization mode setting:<br/>Synchronization signals are input at these pins.<br/>When the RCLK is "H" level and these pins receive an "H" signal in hunting operation, the data sampled at the next rise of RCLK is the starting bit of the receiving data.</li> <li>Internal synchronization mode:<br/>These pins are used as the synchronization character detect output pins. When incoming data</li> </ul>      |

| SYBRK1     | I/O | 53      | Synchronous/Break<br>Detect 1 | <ul> <li>matches the synchronization character register setting (both characters must match in bisynchronous mode), an "H" signal is output here.</li> <li>Next, the status register is read and this signal returns to "L" at the end of the read signal.</li> <li>Asynchronous mode:</li> <li>These pins function as break detect output pins. Immediately after a framing error, an "H" signal is output if all receiving data values (one frame including start bit, parity bit, and stop bit) are "0." This "H" signal is cancelled if a "1" data is received before a reset is applied.</li> </ul> |

| RRDY0      | 0   | 43      | Receive Ready 0               | Receive Ready output pin<br>These pins are "H" level, when serial data received at<br>the RCVDT0, RCVDT1 pins is converted to parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RRDY1      | 0   | 44      | Receive Ready 1               | data in the SDTR module and is in readable form.<br>Then after the received data is read, these pins<br>becomes "L" level at the end of the read signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 5. RCSTG SIGNALS (11)

| Pin symbol | I/O | Pin no. | Pin name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------|-----|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CS0#       | 0   | 16      | Expansion Chip Select 0 | Expansion Chin Salaat autout nin                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CS1#       | 0   | 21      | Expansion Chip Select 1 | Expansion Chip Select output pin<br>When the input to the RCS# pin is "L," one of these                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| CS2#       | 0   | 24      | Expansion Chip Select 2 | chip select signals will be active depending on the                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| CS3#       | 0   | 25      | Expansion Chip Select 3 | combination of input signals to the A0, A1 pins.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RE#        | 0   | 35      | Expansion Read Enable   | Expansion Read Enable output pin<br>When the input to the RCS# pin is "L" and a bus cycle<br>begins with an "H" input to the RD/WR# pin, this pin<br>produces a pulse of the designated width and the<br>designated timing.                                                                                                                                                                                                                                 |  |  |  |

| WE#        | 0   | 36      | Expansion Write Enable  | Expansion Write Enable output pin<br>When the input to the RCS# pin is "L" and a bus cy<br>begins with an "L" input to the RD/WR# pin, this pir<br>produces a pulse of the designated width and the<br>designated timing.                                                                                                                                                                                                                                   |  |  |  |

| DS#        | 0   | 47      | Expansion Data Strobe   | Expansion Data Strobe output pin<br>When a bus cycle begins with the RCS# pin input at<br>"L" level, this pin produces a pulse of the designated<br>width and the designated timing.                                                                                                                                                                                                                                                                        |  |  |  |

| RCS#       | I   | 37      | Resource Chip Select    | Resource Chip Select pin.<br>This pin is used to input the chip select signal supplied<br>to the module RCSTG.<br>When the module RCSTG is used to generate the<br>external resource chip select signals CS0# to CS3#,<br>read strobe RE#, write strobe WE#, and data strobe<br>DS#, the corresponding areas must be decoded.<br>This pin has internal pull-up resistance (MB86941<br>only).                                                                |  |  |  |

| A0         | I   | 38      | Address 0               | These are the input pins for the address signal to the<br>module RCSTG.<br>When the module RCSTG is used to generate the<br>external resource chip select signals CS0# to CS3#,<br>read strobe signal RE#, write strobe signal WE#, and<br>data strobe signal DS#, this address input signal is<br>used to designate the byte position in the                                                                                                               |  |  |  |

| A1         | I   | 39      | Address 1               | corresponding area.<br>When the input to the RCS# pins is "L" level, the input<br>signal to these pins determines which of the external<br>resource chip select signals CS0# to CS3# goes<br>active.<br>These pins have internal pull-up resistance (MB86941<br>only).                                                                                                                                                                                      |  |  |  |

| RDYOUT#    | 0   | 49      | Ready Out               | This is the output pin for the ready signal generated by<br>the module RCSTG.<br>When the module RCSTG is used to generate the<br>external resource chip select signals CS0#-CS3#,<br>read strobe signal RE#, write strobe signal WE#, and<br>data strobe signal DS#, the ready signal is output from<br>these pins to the MPU.<br>When any of the signals CS0# to CS1# is at "L" level,<br>this signal is asserted with the designated timing<br>interval. |  |  |  |

#### 6. I/O PORT SIGNALS (16)

| Pin symbol | I/O | Pin no. | Pin name    | Description                                                                             |

|------------|-----|---------|-------------|-----------------------------------------------------------------------------------------|

| IPD0       | I/O | 72      | I/O Port 0  |                                                                                         |

| IPD1       | I/O | 78      | I/O Port 1  |                                                                                         |

| IPD2       | I/O | 84      | I/O Port 2  |                                                                                         |

| IPD3       | I/O | 85      | I/O Port 3  |                                                                                         |

| IPD4       | I/O | 86      | I/O Port 4  |                                                                                         |

| IPD5       | I/O | 87      | I/O Port 5  |                                                                                         |

| IPD6       | I/O | 94      | I/O Port 6  | Signal I/O port                                                                         |

| IPD7       | I/O | 95      | I/O Port 7  | These pins may be used for input or output, as                                          |

| IPD8       | I/O | 96      | I/O Port 8  | determined by register setting.<br>These pins have internal pull-up resistance (MB86941 |

| IPD9       | I/O | 98      | I/O Port 9  | only).                                                                                  |

| IPD10      | I/O | 99      | I/O Port 10 |                                                                                         |

| IPD11      | I/O | 103     | I/O Port 11 |                                                                                         |

| IPD12      | I/O | 104     | I/O Port 12 |                                                                                         |

| IPD13      | I/O | 105     | I/O Port 13 |                                                                                         |

| IPD14      | I/O | 106     | I/O Port 14 |                                                                                         |

| IPD15      | I/O | 107     | I/O Port 15 |                                                                                         |

#### 7. SIO SIGNALS (4)

| Pin symbol | I/O | Pin no. | Pin name              | Description                                                                                                                                                                                                                                                                                                                                                  |

|------------|-----|---------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SICLK      | 1/0 | 114     | SIO Clock             | This is the input/output pin for the clock signal used for<br>SIO serial data transfer.<br>In external clock mode, the clock signal for serial data<br>transfer is input at this pin.<br>In internal clock mode, the clock signal from the<br>internal clock generator is output at this pin.<br>This pin has internal pull-up resistance (MB86941<br>only). |

| SIRXD      | I   | 109     | SIO Receive Data      | SIO Receive Data input pin<br>This pin receives data input LSB first, synchronously<br>with the SICLK pin clock signal. This pin has internal<br>pull-up resistance (MB86941 only).                                                                                                                                                                          |

| SITXD      | 0   | 110     | SIO Transmit Data     | SIO Transmit Data output pin<br>This pin outputs data LSB first, synchronously with the<br>SICLK pin clock signal.                                                                                                                                                                                                                                           |

| SIIRQ      | 0   | 111     | SIO Interrupt Request | SIO Interrupt Request output pin                                                                                                                                                                                                                                                                                                                             |

#### 8. VDD, Vss, N.C. (24/25)

| Pin symbol | I/O | Pin no.                                                             | Pin name | Description                                                                         |

|------------|-----|---------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------|

| VDD        | _   | 1, 18,<br>54, 73,<br>90, 126                                        |          | Power supply input pin                                                              |

| Vss        |     | 9, 19,<br>30, 45,<br>55, 66,<br>81, 91,<br>102,<br>117,<br>127, 138 |          | Grand pin                                                                           |

| N.C.       |     | 97, 108,<br>112,<br>115,<br>116, 123<br>(17*)                       |          | These pins shall be used as an open pin.<br>No. 17 is also an open pin for MB86942. |

\* : No.17 is a READY2# pin for MB86941.

#### ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol | Rating                                      |        |                                |         |                   |            | l lasit |

|----------------------|--------|---------------------------------------------|--------|--------------------------------|---------|-------------------|------------|---------|

| Parameter            | Symbol | MB86941                                     |        |                                | MB8     | Unit              |            |         |

| Power supply voltage | VDD    | _                                           | 0.5 to | 0 +0.6*1                       |         | –0.5 to           | +4.0*1     | V       |

| Input voltage        | V      |                                             |        | -0                             | .5 to V | 0.5 <sup>*1</sup> |            | V       |

| Output voltage       | Vo     | -0.3 to V <sub>DD</sub> + 0.5 <sup>*1</sup> |        |                                |         | –0.5 to V         | DD + 0.5*1 | ~       |

| Storage temperature  | Tstg   |                                             |        |                                | —40 to  | o 125             |            | °C      |

|                      |        |                                             | *3     | $V_{O} = V_{DD}$               | +40     | Vo = VDD          | +60        |         |

|                      |        |                                             |        | Vo = 0                         | -40     |                   |            |         |

| Output current*2     | 6      | At<br>maximum                               | *4     | $V_{O} = V_{DD}$               | +80     |                   |            | mA      |

|                      |        | VDD                                         | 4      | Vo = 0                         | -40     |                   |            |         |

|                      |        |                                             | *5     | $V_{\text{O}} = V_{\text{DD}}$ | +120    | Vo = 0            | -60        |         |

|                      |        |                                             | 5      | Vo = 0                         | -80     |                   |            |         |

\*1: Vss = 0 V

\*2: At 1 pin for 1 second

\*3: Output pins other than D < 15 : 0 >, READY1# and REDY2#

\*4: D < 15:0 >

\*5: READY1#, READY2#

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Devemeter             | Symphol | Value        |              |      |  |  |

|-----------------------|---------|--------------|--------------|------|--|--|

| Parameter             | Symbol  | MB86941      | MB86942      | Unit |  |  |

| Power supply voltage  | Vdd     | 4.75 to 5.25 | 3.15 to 3.45 | V    |  |  |

| Operating temperature | Та      | 0 to         | °C           |      |  |  |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### ■ ELECTRIC CHARACTERISTICS

#### 1. DC Characteristics

(1) Input Characteristics

| (MB86942: V <sub>DD</sub> = 3.3 V ± 0.15 V, T <sub>A</sub> = 0 to +7 |                                                   |               |      |      |                     |            |      |  |

|----------------------------------------------------------------------|---------------------------------------------------|---------------|------|------|---------------------|------------|------|--|

| Parameter                                                            | Symbol                                            | Condition     | MB8  | 6941 | MB8                 | Linit      |      |  |

|                                                                      | Symbol                                            |               | Min. | Max. | Min.                | Max.       | Unit |  |

|                                                                      | e VIH CLOCK 2.8<br>IRQ15 to IRQ1 2.4<br>Other 2.2 |               | 2.8  | VDD  |                     |            |      |  |

| "H" level input voltage                                              |                                                   | IRQ15 to IRQ1 | 2.4  | VDD  | $V_{DD} 	imes 0.65$ | VDD + 0.15 | v    |  |

|                                                                      |                                                   | Other         | 2.2  | VDD  |                     |            |      |  |

| "L" level input voltage                                              |                                                   | IRQ15 to IRQ1 | Vss  | 0.6  | Vss                 | N          | v    |  |

|                                                                      | V⊫                                                | Other         | Vss  | 0.8  | V SS                | VDD × 0.25 | V    |  |

(2) Output Characteristics

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C)

| Parameter                   | Cumhal     |                                       | MB8  | MB86941     |         | MB86942 |      |

|-----------------------------|------------|---------------------------------------|------|-------------|---------|---------|------|

|                             | Symbol     | Condition                             | Min. | Max.        | Min.    | Max.    | Unit |

|                             |            | I <sub>он</sub> = -8 mA* <sup>2</sup> | 4.0  | VDD         |         |         |      |

| "H" level output<br>voltage | output Von | Iон = -3.2 mA* <sup>3</sup>           | 4.0  | <b>V</b> DD |         |         | V    |

| Voltage                     |            | Iон =4 mA*4                           | _    |             | VDD-0.5 | Vdd     |      |

|                             |            | lo∟ = +12 mA*1                        | Vss  |             |         | _       |      |

| "L" level output voltage    | Mar        | lo∟ = +8 mA*2                         |      | 0.4         | _       |         | v    |

|                             | Vo∟        | lo∟ = +3.2 mA* <sup>3</sup>           |      |             |         |         | V    |

|                             |            | lo∟ = +4 mA*4                         |      |             | Vss     | 0.4     | ]    |

\*1: MB86941 READY1#, READY2#

\*2: MB86941 D < 15 : 0 >

\*3: MB86941 Other than READY1#, READY2# and D < 15 : 0 >

\*4: MB86942

(3) Power Supply Current

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V + 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| Parameter            | Symbol     | Symbol Condition | MB8  | 6941 | MB8  | Unit |      |  |  |

|----------------------|------------|------------------|------|------|------|------|------|--|--|

|                      | Symbol Cor | Condition        | Min. | Max. | Min. | Max. | Unit |  |  |

| Power supply current | lcc        |                  | _    | 230  | _    | 190  | mA   |  |  |

#### 2. Capacitances

| $(V_{DD} = V_1 = 0 V, f = 1 MHz, T_A = +25^{\circ}C$ |              |      |       |      |  |  |  |  |

|------------------------------------------------------|--------------|------|-------|------|--|--|--|--|

| Parameter                                            | Symbol       | v    | Value |      |  |  |  |  |

|                                                      | Symbol       | Min. | Max.  | Unit |  |  |  |  |

| Input Capacitance                                    | Сім          | —    | 16    | pF   |  |  |  |  |

| Output Capacitance                                   | Соит         | —    | 16    | pF   |  |  |  |  |

| I/O Capacitance                                      | <b>C</b> ı/o |      | 16    | pF   |  |  |  |  |

#### 3. AC Test Conditions

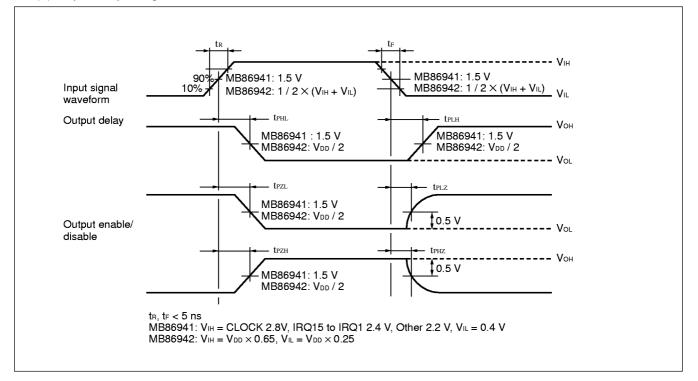

(1) Input/Output Signal Waveform

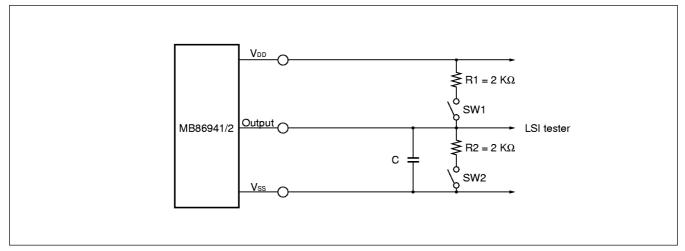

#### (2) Load Circuit

| Condition                           | Load capacitance |         |  |  |  |

|-------------------------------------|------------------|---------|--|--|--|

| Condition                           | MB86941          | MB86942 |  |  |  |

| Normal output                       | 60 pF            | 30 pF   |  |  |  |

| Tri-state output (READY1#, READY2#) | 65 pF            | —       |  |  |  |

| Bi-directional pin (D bus)          | 85 pF            | 30 pF   |  |  |  |

| Signal transmit                    | SW1 | SW2 |

|------------------------------------|-----|-----|

| $L \rightarrow H, H \rightarrow L$ | OFF | OFF |

| $L \rightarrow Z, Z \rightarrow L$ | ON  | OFF |

| $L \rightarrow Z, Z \rightarrow L$ | OFF | ON  |

#### 4. AC Characteristics

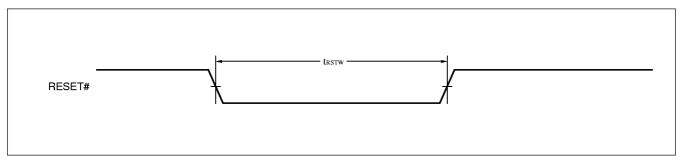

(1) Reset signal (Hardware reset)

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| Parameter         | Symbol        | Va   | Unit |              |

|-------------------|---------------|------|------|--------------|

| Falailletei       | Symbol        | Min. | Max. | Onit         |

| Reset pulse width | <b>t</b> rstw | 20   | —    | <b>t</b> clk |

tclk: See "(2) Clock Signals."

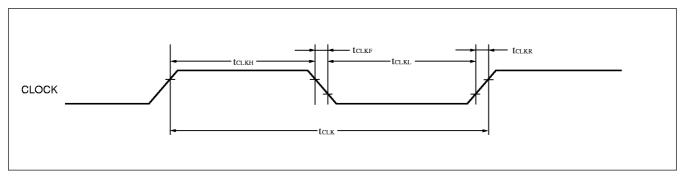

#### (2) Clock signal (CLOCK)

#### (MB86941: $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| Parameter             | Symbol        | MB8  | 6941 | MB8  | 6942 | Unit |  |  |  |  |

|-----------------------|---------------|------|------|------|------|------|--|--|--|--|

| Falalletei            | Symbol        | Min. | Max. | Min. | Max. | Unit |  |  |  |  |

| Clock cycle time      | <b>t</b> c∟ĸ  | 25   | —    | 20   | —    | ns   |  |  |  |  |

| Clock "H" pulse width | <b>t</b> clkh | 9    | _    | 8    | _    | ns   |  |  |  |  |

| Clock "L" pulse width | <b>t</b> clkl | 9    | _    | 8    | _    | ns   |  |  |  |  |

| Clock rise time       | <b>t</b> clkr | _    | 4    | —    | 2    | ns   |  |  |  |  |

| Clock fall time       |               |      | 4    | _    | 2    | ns   |  |  |  |  |

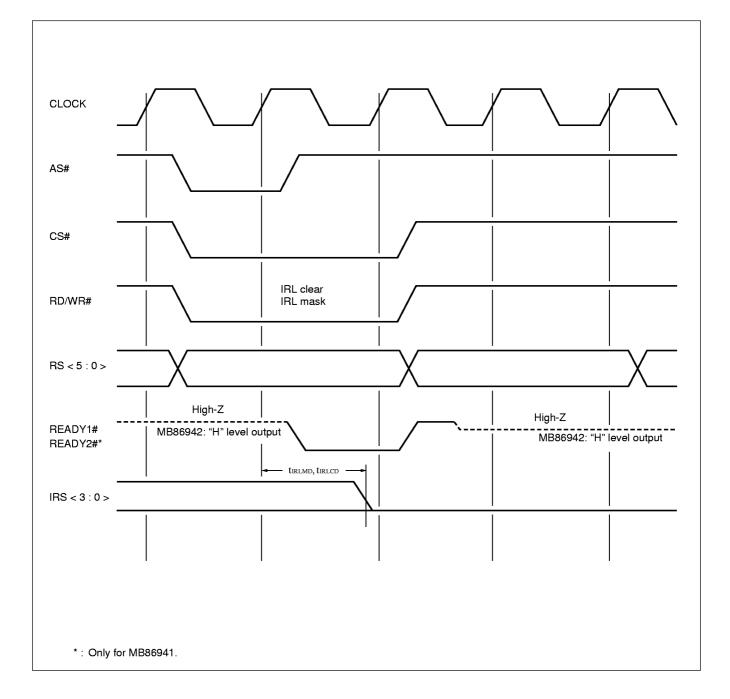

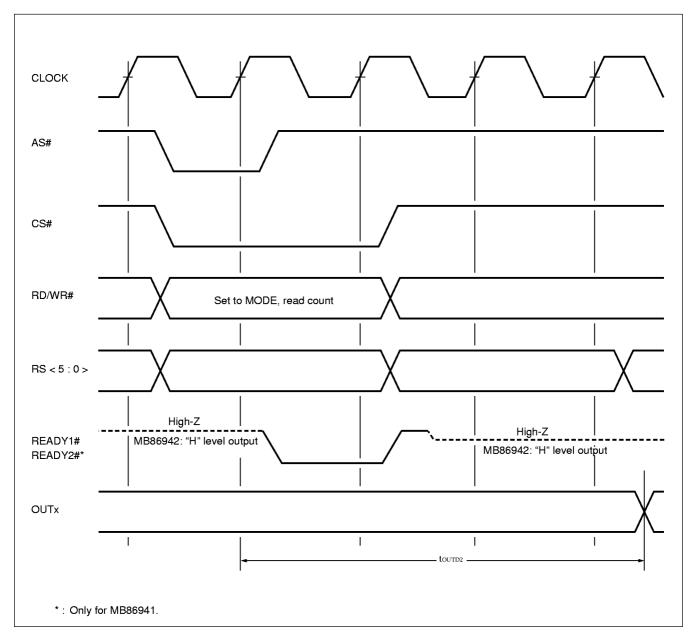

(3) MPU interface (Register read/write)

|                                           |               | <u>را</u> | VID0034 | - <b>Z. V</b> DD - | - 0.0 V - | 0.15 0  | , TA – U | to $+/0^{\circ}C$ ) |

|-------------------------------------------|---------------|-----------|---------|--------------------|-----------|---------|----------|---------------------|

|                                           |               |           | MB8     | 6941               | MB86942   |         |          |                     |

| Parameter                                 | Symbol        | WSEL      | = "H"   | WSEL               | . = "L"   | WD00942 |          | Unit                |

|                                           |               | Min.      | Max.    | Min.               | Max.      | Min.    | Max.     |                     |

| AS# setup time                            | tass          | 11        |         | 7                  | _         | 7       | _        | ns                  |

| AS# hold time                             | <b>t</b> ash  | 0         | _       | 0                  | _         | 2       |          | ns                  |

| CS# setup time                            | tcss          | 8         | _       | 5                  | _         | 7       | _        | ns                  |

| CS# hold time                             | tcsH          | 0         | _       | 0                  |           | 2       | _        | ns                  |

| RD/WR# setup time                         | trws          | 13        |         | 9                  | _         | 7       | _        | ns                  |

| RD/WR# hold time                          | <b>t</b> RWH  | 0         | _       | 0                  | _         | 2       | _        | ns                  |

| RS < 5 : 0 > setup time                   | trss          | 8         | _       | 5                  | _         | 7       | _        | ns                  |

| RS < 5 : 0 > hold time                    | <b>t</b> RSH  | 0         |         | 0                  | _         | 2       | _        | ns                  |

| READY1#, READY2# output delay time        | <b>t</b> RDYF | 0         | 18      | 0                  | 18        | 0       | 18       | ns                  |

| READY1#, READY2# hold time                | <b>t</b> rdyh | 5         | 20      | 5                  | 20        | 5       | 20       | ns                  |

| D < 15 : 0 > Output delay time at reading | todd          | 0         | 21      | 0                  | 23        | 0       | 23       | ns                  |

| D < 15 : 0 > Output hold time at reading  | todh          | 5         | 25      | 5                  | 25        | 5       | 20       | ns                  |

| D < 15 : 0 > Input setup time at writing  | tids          | 11        | —       | 7                  |           | 7       |          | ns                  |

| D < 15 : 0 > Input hold time at writing   | <b>t</b> IDH  | 0         |         | 0                  |           | 0       |          | ns                  |

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

\* : READY2# is available for MB86941.

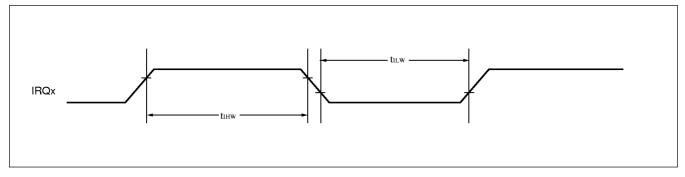

- (4) Interrupt signal

- · Interrupt input pulse width

| (MB86941: VDD = 5 V $\pm$ 5%, TA = 0 to +70°C)                        |

|-----------------------------------------------------------------------|

| (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ , $T_A = 0$ to $+70^{\circ}C$ ) |

| $(101080342, 000 = 3.3, 0 \pm 0.13, 0, 14 = 0.10, 170, 0)$ |        |             |      |      |  |  |  |

|------------------------------------------------------------|--------|-------------|------|------|--|--|--|

| Parameter                                                  | Symbol | Va          | Unit |      |  |  |  |

|                                                            | Symbol | Min.        | Max. | Unit |  |  |  |

| IRQ input "H" level pulse width*1                          | tıнw   | 6 tськ + 10 | _    | ns   |  |  |  |

| IRQ input "L" level pulse width*2                          | tı∟w   | 6 tolk + 10 | _    | ns   |  |  |  |

tclk: See "(2) Clock Signals."

\*1: When the trigger mode is set for "H" level signal input or RISE-EDGE, a pulse of at least this width is received as a REQ-FF signal. Note that this rule does not guarantee that no interrupts less than this width will be received.

\*2: When the trigger mode is set for "L" level signal input or FALL-EDGE, a pulse of at least this width is received as a REQ-FF signal. Note that this rule does not guarantee that no interrupts less than this width will be received.

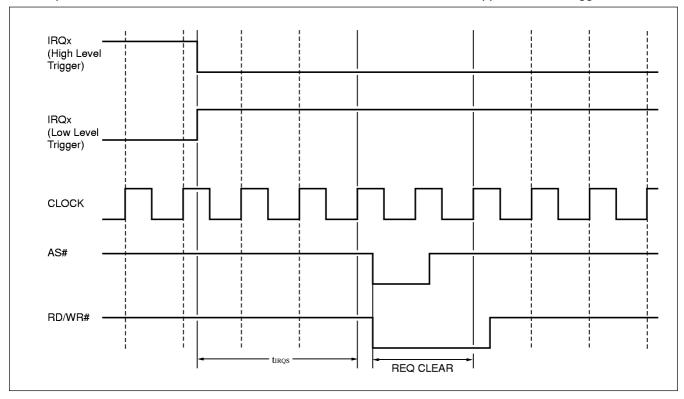

· Interrupt input clear

|                        | (MB86941: $V_{DD}$ = 5 V ± 5%, T <sub>A</sub> = 0 to +70°C<br>(MB86942: $V_{DD}$ = 3.3 V ± 0.15 V, T <sub>A</sub> = 0 to +70°C |             |      |      |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|

| Parameter              | Symbol                                                                                                                         | Value       |      | Unit |

|                        | Symbol                                                                                                                         | Min.        | Max. | Onit |

| IRQx clear setup time* | tiras                                                                                                                          | 2 tclk + 10 | _    | ns   |

tolk: See "(2) Clock Signals."

\* : This parameter means the condition of REQUEST CLEAR execution and is applied at level trigger modes.

Interrupt level output

#### (MB86941: $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| Parameter                      | Cumphiel       | Va   | ´    |      |

|--------------------------------|----------------|------|------|------|

|                                | Symbol         | Min. | Max. | Unit |

| IRL < 3 : 0 > clear delay time |                | —    | 80   | ns   |

| IRL < 3 : 0 > mask delay time  | <b>t</b> irlmd | _    | 80   | ns   |

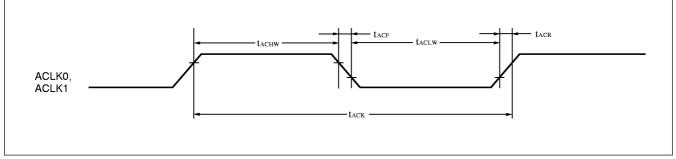

- (5) Prescaler timer

- · Prescaler input

| (MB86941: $V_{DD} = 5 V \pm 5\%$ ,      | $T_{A} = 0 \text{ to } +70^{\circ}\text{C}$ |

|-----------------------------------------|---------------------------------------------|

| (MB86942; $V_{DD} = 3.3 V \pm 0.15 V$ . | $T_{A} = 0 \text{ to } +70^{\circ}\text{C}$ |

| $(VID80942, VDD = 3.5 V \pm 0.13 V, IA = 0 t0 + 70 G)$ |               |      |      |      |       |      |  |

|--------------------------------------------------------|---------------|------|------|------|-------|------|--|

| Parameter                                              | Symbol        | MB8  | 6941 | MB8  | Llmit |      |  |

|                                                        | Symbol        | Min. | Max. | Min. | Max.  | Unit |  |

| Prescaler input clock cycle time*                      | tаск          | 50   | —    | 40   | —     | ns   |  |

| Prescaler input clock "H" level width*                 | <b>t</b> achw | 22   | _    | 15   | _     | ns   |  |

| Prescaler input clock "L" level width*                 | <b>t</b> aclw | 22   | —    | 15   | —     | ns   |  |

| Prescaler input clock rise time*                       | <b>t</b> acr  |      | 5    | _    | 5     | ns   |  |

| Prescaler input clock fall time*                       | <b>t</b> ACF  |      | 5    | _    | 5     | ns   |  |

\* : Applied in prescaler external clock mode. When the prescaler output is used as a timer signal, the timer input clock requirements must be met.

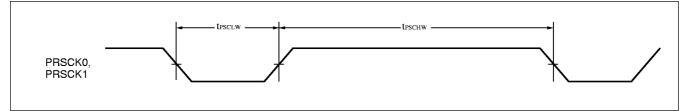

• Prescaler output

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| $(VIB80942. VDD = 3.3 V \pm 0.13 V, TA = 0.10$ |                |                        |                            |  |  |

|------------------------------------------------|----------------|------------------------|----------------------------|--|--|

| Parameter                                      | Symbol         | Standard Value         | Unit                       |  |  |

| Prescaler output "L" level width*1, *3         | <b>t</b> PSCLW | 1                      | <b>t</b> pck <sup>*4</sup> |  |  |

| Prescaler output "H" level width*1, *3         | <b>t</b> PSCHW | N – 1                  | tpck*4                     |  |  |

| Prescaler output "L" level width*2, *3         | <b>t</b> PSCLW | N · 2 <sup>M − 1</sup> | <b>t</b> PCK <sup>*4</sup> |  |  |

| Prescaler output "H" level width*2, *3         | <b>t</b> PSCHW | N · 2 <sup>M−1</sup>   | <b>t</b> PCK <sup>*4</sup> |  |  |

\*1: Applied when the prescaler register SELECT field is set to "0." N: Value set in the prescaler register PRESCALE VALUE field

- \*2: Applied when the prescaler register SELECT field is set to any value other than "0." M: Value set in the prescaler register SELECT field.

- N: Value set in the prescaler register PRESCALE VALUE field.

- \*3: When the prescaler register SELECT field is set to "0," the PRSCKx output is fixed at "L" level.

- \*4: tPCK has the following prescaler input clock period. Internal clock mode: tPCK = 2 · tCLK (For tCLK, see "(2) Clock Signals") External clock mode: tPCK = tACK (For tACK, see "(5) Prescaler Timer Unit/Prescaler Input")

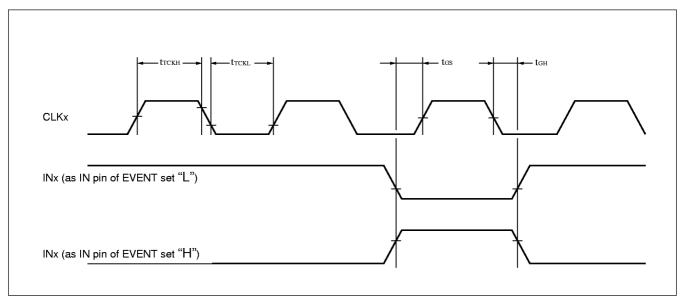

• Timer (at external clock mode)

#### (MB86941: $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| _                                          |                 | Va   |      |              |

|--------------------------------------------|-----------------|------|------|--------------|

| Parameter                                  | Symbol          | Min. | Max. | Unit         |

| Timer input clock "H" level width          | <b>t</b> тскн   | 3    |      | <b>t</b> c∟ĸ |

| Timer input clock "L" level width          | tтск∟           | 3    |      | tclk         |

| GATE signal (IN pin) setup time (for CLKx) | tas             | 10   |      | ns           |

| GATE signal (IN pin) hold time (for CLKx)  | t <sub>GH</sub> | 0    |      | ns           |

tclk: See "(2) Clock Signals".

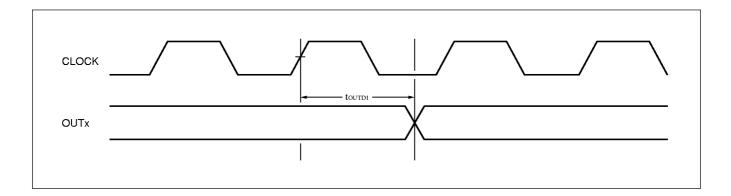

• Timer output 1

(MB86941:  $V_{DD} = 5 V \pm 5\%$ ,  $T_A = 0$  to  $+70^{\circ}$ C)

| (MB86942: VDD = $3.3 \text{ V} \pm 0.15 \text{ V}$ , TA = 0 to +70°C | ) |

|----------------------------------------------------------------------|---|

|----------------------------------------------------------------------|---|

| Parameter                         | Symbol | Value |      | Unit |

|-----------------------------------|--------|-------|------|------|

|                                   | Symbol | Min.  | Max. | Unit |

| OUT output delay time (for CLOCK) | toutd1 | —     | 30   | ns   |

• Timer output 2

(MB86941:  $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942:  $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| $(MB00942. VDD = 3.3 V \pm 0.15 V, TA = 0.10 + 70 C)$ |        |       |             |       |  |

|-------------------------------------------------------|--------|-------|-------------|-------|--|

| Parameter                                             | Symbol | Value |             | llait |  |

|                                                       | Symbol | Min.  | Max.        | Unit  |  |

| OUT output delay time*                                | toutd2 | _     | 3 tськ + 30 | ns    |  |

tolk: See "(2) Clock Signals".

\* : Applied to the following cases.

- Setting mode (write to TCR).

- After setting to MODE0, write to RELOAD register/read COUNT register.

- After setting to MODE1, write to RELOAD register/read COUNT register.

- After setting to MODE3, write to RELOAD register.

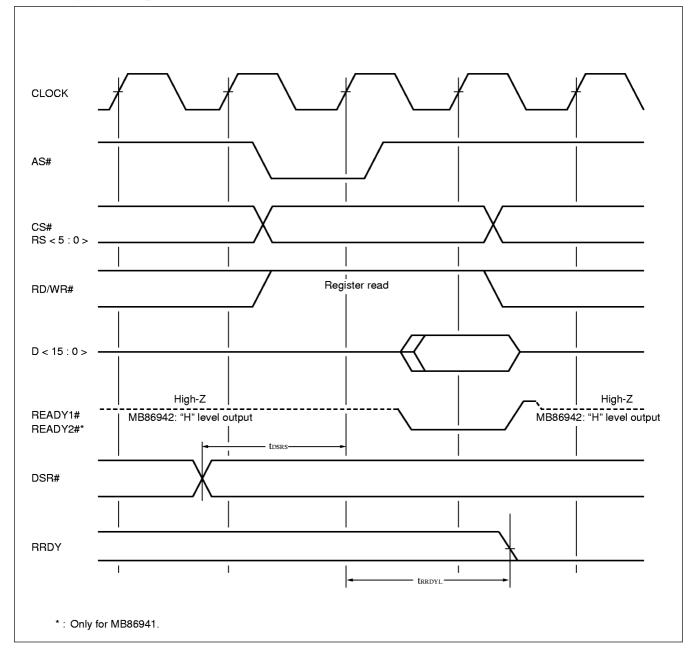

- (6) SDTR

- DSR#, RRDY

#### (MB86941: $V_{DD} = 5 V \pm 5\%$ , T<sub>A</sub> = 0 to +70°C) (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ , T<sub>A</sub> = 0 to +70°C)

| Deremeter                               | Symbol        | Va   | 11   |              |

|-----------------------------------------|---------------|------|------|--------------|

| Parameter                               | Symbol        | Min. | Max. | Unit         |

| DSR# setup time for resistor read       | <b>t</b> dsrs | 28   | _    | <b>t</b> clk |

| Interval from register read to RRDY off |               | 0    | 100  | ns           |

tclk: See "(2) Clock Signals".

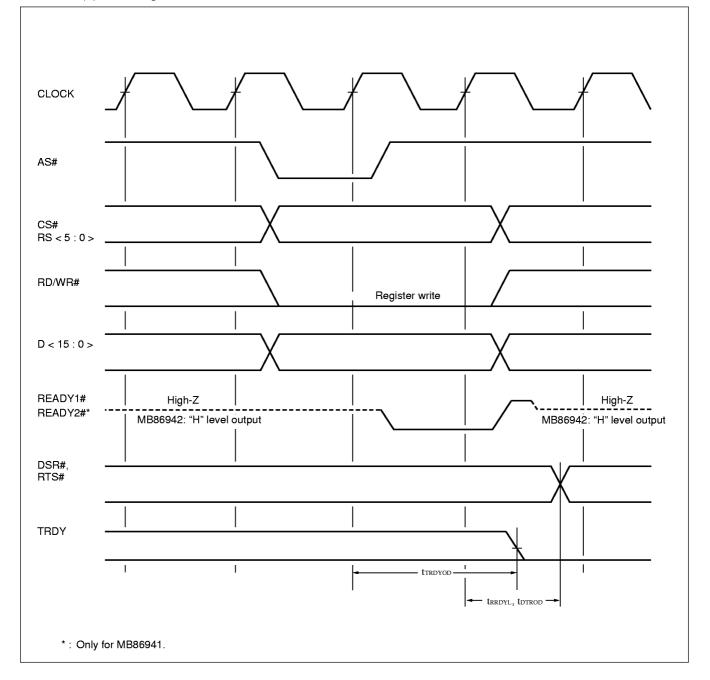

#### • DTR#, RTS#, TRDY

| (MB86941: $V_{DD} = 5 V \pm 5\%$ , $T_A = 0 \text{ to } +70^{\circ}\text{C}$ ) |  |

|--------------------------------------------------------------------------------|--|

| (MB86942: $V_{DD} = 3.3 V \pm 0.15 V$ . T <sub>A</sub> = 0 to +70°C)           |  |

| Devementer                                    | Symbol –        | Va   | llait |              |

|-----------------------------------------------|-----------------|------|-------|--------------|

| Parameter                                     |                 | Min. | Max.  | Unit         |

| Delay time from register write to DTR# output | <b>t</b> dtrod  | 0    | 40    | <b>t</b> clk |

| Delay time from register write to RTS# output | <b>t</b> rtsod  | 0    | 40    | <b>t</b> clk |

| Delay time from register write to TRDY output | <b>t</b> trdyod | 0    | 100   | ns           |

tolk: See "(2) Clock Signals".

Command write cycle

| (MB86941: $V_{DD} = 5 V \pm 5\%$ , $T_A = 0$ to $+70^{\circ}C$                               | ) |

|----------------------------------------------------------------------------------------------|---|

| (MB86942: V <sub>DD</sub> = $3.3 \text{ V} \pm 0.15 \text{ V}$ , T <sub>A</sub> = 0 to +70°C | ) |

| Deveneter                                          | Overshell      | Value |      | Unit         |  |

|----------------------------------------------------|----------------|-------|------|--------------|--|

| Parameter                                          | Symbol Min. Ma |       | Max. |              |  |

| Command write cycle time (for initial value setup) | <b>t</b> CMDC  | 14    | _    | <b>t</b> clk |  |

| Command write cycle time (for asynchronous mode)   | tcmdc          | 20    | _    | <b>t</b> clk |  |

| Command write cycle time (for synchronous mode)    | tсмрс          | 40    | _    | <b>t</b> clk |  |

tclk: See "(2) Clock Signals".

(MB86941:  $V_{DD} = 5 V \pm 5\%$ ,  $T_A = 0 \text{ to } +70^{\circ}\text{C}$ )

Transmit Clock and Transmit Data

| (MB86942: $V_{DD}$ = 3.3 V ± 0.15 V, T <sub>A</sub> = 0 to +70°C) |                        |            |              |                   |      |              |  |

|-------------------------------------------------------------------|------------------------|------------|--------------|-------------------|------|--------------|--|

| Deveneter                                                         | 0 milion               | Syncroh mo | de, × 1 mode | ×1/16, ×1/64 mode |      |              |  |

| Parameter                                                         | Symbol                 | Min.       | Max.         | Min.              | Max. | Unit         |  |

| Transmit Clock "H" width                                          | <b>t</b> тскн <b>w</b> | 32         | —            | 4                 | _    | <b>t</b> clk |  |